Wat is het tegenovergesteld van een logic analyser? Of eigenlijk “complementair aanvullend”, zoals een PNP en NPN transistor of een functie-generator en een oscilloscoop? Het blijkt een pattern generator te heten. Een soort digitale AWG dus.

Zulk een ding is handig om een-of-ander digitaal signaal te genereren, bijvoorbeeld om te testen hoe een (deel)systeem daar op reageert. Concreet voorbeeld: het testen van een displaytje waarbij het te ingewikkeld wordt dat met de hand te doen.

Ook zou je, voor de gein, iets kunnen maken dat een tekst weergeeft wanneer je met een logic analyser naar het gegenereerde patroon kijkt.

Ik maakte dit door met de PIO van een raspberry pi pico het gewenste patroon uit te sturen. Het patroon staat in RAM (en kan dus runtime gewijzigd worden). Het bestaat uit een opeenvolging van gewenste uitgangswaarden en wachttijden.

uint32_t pattern[SIZE] =

{0xFFFF, 5, 0x0000, 25,

0xFF, 2, 0x18, 3, 0xFF, 2, //H

0x00, 3,

0xFF, 1, 0x99, 3, // E

0x00, 3,

0xFF, 1, 0x80, 3, // L

0x00, 3,

0xff, 1, 0x80, 3, // L

0x00, 3,

0xff, 1, 0x81, 2, 0xff, 1 // O

};De PIO speelt dit af met het volgende programma:

.wrap_target

out pins 32

out x 32

waitlbl:

jmp x-- waitlbl

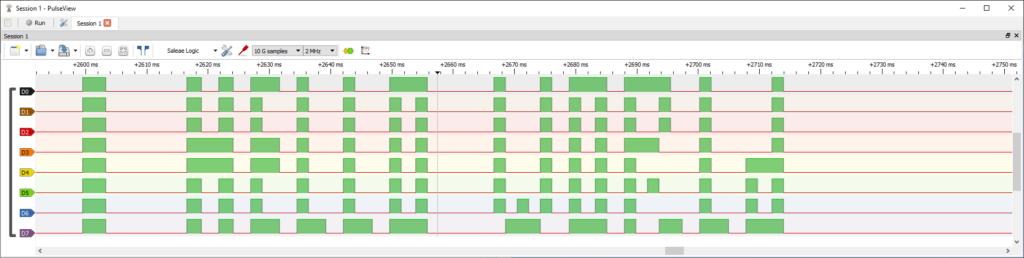

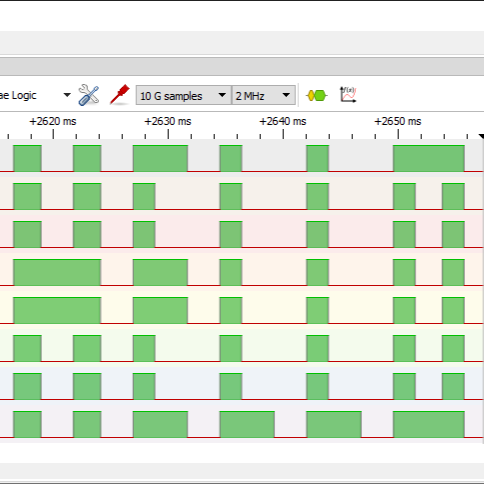

.wrap Omdat mijn logic analyser slechts 8 kanalen heeft gebruik ik alleen de 8 LSB. Ook loopt de pico niet op maximale snelheid, anders kan mijn logic analyser het niet bijhouden1. Op hogere snelheden is te zien dat de LA af en toe een stukje mist2 (Klik om de afbeelding op groot formaat te zien):

Om er een nuttig bruikbare patroongenerator van te maken moet er nog iets bij om makkelijk het patroon te kunnen wijzigen. Het patroon in ram wijzigen via de debugger werkt wel, maar vind ik in de praktijk toch erg omslachtig. Ook zou het handig zijn als er een mogelijkheid was om kloksignalen te maken3.

Ik ga dat nu niet doen, maar misschien is dit desondanks nuttig voor iemand, bijvoorbeeld als onderdeel van een groter project, om met weinig PIO-instructies complexe digitale signalen uit te sturen.

De complete broncode is te vinden in deze git gist.

Voetnootjes

- Je kunt er dus ook de maximum samplesnelheid van je Logic Analyser mee controleren 🙂 ↩︎

- Kun je dat “De flank misslaan” noemen? Van klokflank. En dan te bedenken dat “de plank misslaan” al een combinatie van 2 uitdrukkingen is. ↩︎

- Kloktikken maken kan nu wel, maar kost 4 uint32_t’s per klokslag: Hoog, delay, laag, delay. En kost dus relatief veel geheugen. Een ‘Doe eens NN kloktikken op pinnetje ZusOfZo’ zou praktisch zijn wanneer meerdere klokslagen de data niet wijzigt. ↩︎

Leave a Reply